This blog originally ran on the Antmicro website. For more blogs and articles like this one, visit https://antmicro.com/blog/.

The virtual RISC-V Summit on December 8-10, 2020 put a spotlight on a range of interesting, real-life use cases and implementations of the groundbreaking open source processor architecture, with a number of informative talks to be given by thought leaders who will be sharing their ideas, goals and achievements within the area of RISC-V system design and tooling. Antmicro’s activity in this space hasn’t slowed down, and, as a Strategic Founding Member of RISC-V International, we featured a diverse range of RISC-V-related services, participated a keynote session that included our partners and RISC-V International members, and gave talks describing our efforts aimed at improving the RISC-V tooling ecosystem.

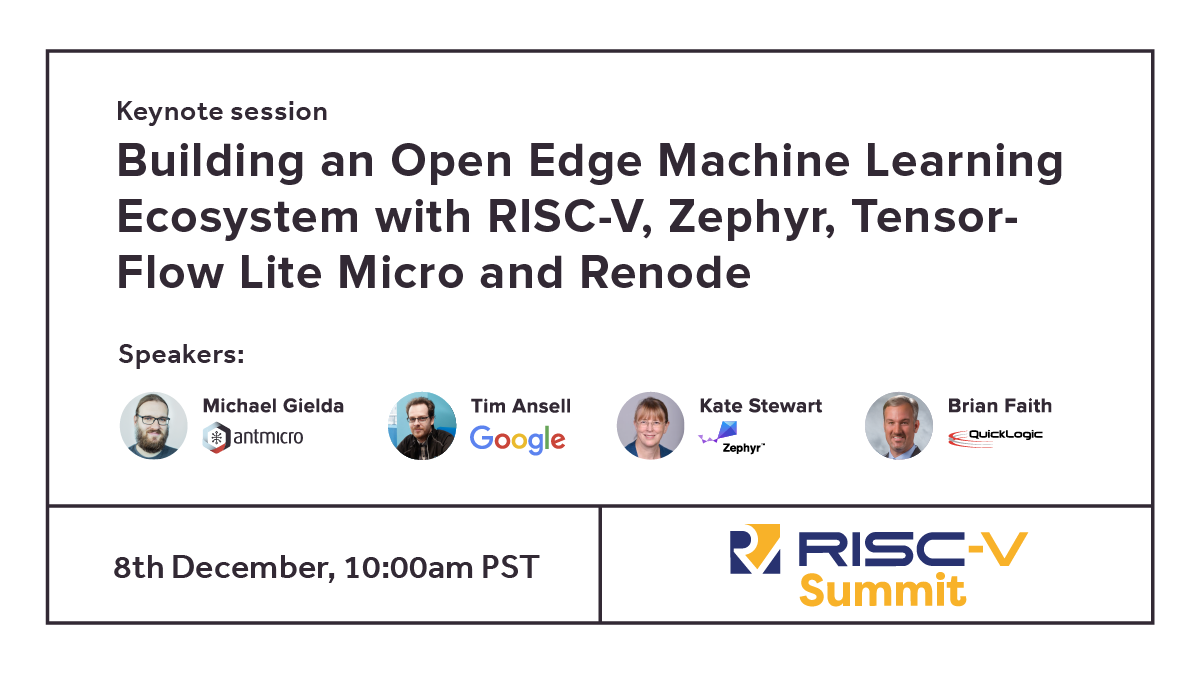

On December 8, Antmicro’s Michael Gielda moderated the keynote session entitled “Building an Open Edge Machine Learning Ecosystem with RISC-V, Zephyr, TensorFlow Lite Micro and Renode”, that also featured Google’s Tim Ansell, QuickLogic’s Brian Faith and the Linux Foundation’s Kate Stewart. The discussion revolved around a number of technologies we are integrating to push ML on RISC-V forward, and how to create testable and measureable development flows using Renode.

Also, Antmicro’s tech leads gave two talks describing our efforts focusing on building an open source SystemVerilog ecosystem and explaining how Renode can be used with LiteX to enable a modular approach to system design. If you attended RISC-V Summit but missed these sessions, all presentations are available on-demand on the conference platform until March 12, 2021. If you didn’t attend the conference, stay tuned. The videos will be posted on the RISC-V Youtube Channel shortly after the platform closes.

Wide-ranging RISC-V efforts

For the past year, we’ve been working on a large number of RISC-V based projects, using the ISA to build various practical systems, as well as developing open source tools, IP and integrations to enhance the ecosystem.

One of the areas where RISC-V has been delivering great results is TinyML, where the ability to customize the architecture and build AI-optimized CPUs without having to acquire an ISA license has been spurring incredible innovations around the globe. In collaboration with Google we have been helping to port TensorFlow Lite Micro onto RISC-V and make it work with new platforms, as well as building dedicated Continuous Integration infrastructure using our open source simulator for system design and testing, Renode. It’s an exciting development that demonstrates RISC-V as a robust base for TinyML applications, with Renode providing a flexible system development environment.

Earlier this year, we had used an excellent RISC-V implementation called VexRiscv to showcase TF Lite running on an FPGA, and we are pursuing multiple projects related to open source AI acceleration on FPGA which is a very promising field, especially given our involvement with open source FPGA tooling which can be used to co-develop AI capabilities between hardware and software.

The flexibility of FPGAs and VexRiscv is also showcased by a separate effort by Antmicro – extending the CPU with multi-core functionality, to provide additional computing power and versatility for this open and flexible 32-bit RISC-V implementation. For the first time in history, relatively small FPGAs have been shown as capable of running multi-core Linux and other software-intensive workloads executed entirely in an FPGA.

We’d also been pretty involved with RISC-V in the area of security, and you can see our tools gaining momentum in that space. Renode has been used for running the seL4 microkernel on some RISC-V implementations. seL4 is the world’s only microkernel with formal verification and is in use in real-life systems of our customers, where it handles classified military information and prevents attacks on unmanned vehicles. Now, Renode enables accelerated development and comprehensive testing of various security-oriented devices based on RISC-V and seL4.

Staying within the domain of security, Renode is also being used in the development of Precursor, an excellent security-oriented messaging device based on RISC-V. If you are into security and privacy, and have not yet preordered this FPGA-based security development platform, be sure to do so on CrowdSupply before the campaign ends!

Delving further into the RISC-V based chip development space, in 2020 we also released the GEM1 and GEM2 chiplet-based designs as open source, with the younger of the siblings – GEM2 – featuring an eFabless’s RISC-V MCU, Ravenna. We’re also continuing on that route with our partners, taking part in Google-sponsored SkyWater open source PDK shuttle run. Our ASIC and SiP efforts involving RISC-V are gaining momentum so stay tuned for more updates.

Tooling and ecosystem

Lots of our RISC-V work focuses on the overall tooling ecosystem for open source development. Throughout 2020, we have been expanding RISC-V support in Renode, developing open source ASIC and FPGA tools, creating portable, vendor-neutral FPGA IPs, and enabling software support for RISC-V-based platforms.

Recent Renode upgrades have brought a range of RISC-V ecosystem improvements. Our simulator now features vastly improved support for CSRs and custom instructions, more instruction set disassembly capabilities, and improved support for multiple RISC-V platforms including the long-awaited PolarFire FPGA SoC Icicle Kit.

Together with companies like Google, Western Digital and QuickLogic, as well as the broader ecosystem of CHIPS Alliance (of which we are a Platinum Member) we’ve been developing open source tools for CI-driven flows in hardware development, including SystemVerilog and UVM support in Yosys and Verilator to enable design verification for real-world applications. Moreover, we’ve been working on improving Surelog – a multi-purpose SystemVerilog parser. Besides working with the parser itself, we’ve been pushing forward its integration with Yosys and Verilator. The integration is being done using Universal Hardware Data Model (UHDM), which we also improve along the way.

Many of our customer projects involve soft RISC-V SoCs and various I/O IPs. That is why we have been continuing to develop and enhance various vendor-neutral and reusable FPGA IPs, such as MIPI CSI, MIDI, PCIe, USB and Ethernet. For similar reasons, we have created a test suite for comparing multiple soft CPUs, including a number of RISC-V implementation, which allows a quick comparison of different CPUs to determine which one is the best for a specific customer scenario.

Get in touch with us at contact@antmicro.com to find out how our end-to-end system and tooling development services can help you achieve your goals.